# 4-WAY SUPERSCALAR + VECTOR-REGISTER PROCESSOR/DESIGN with Parallel Neuron Transfer Functions Austin Brendle, Parker Tribble, Freddie Sanchez Govea/

ELIZABETHTOWN COLLEGE

## MAIN DESIGN

Joseph T. Wunderlich Ph.D.

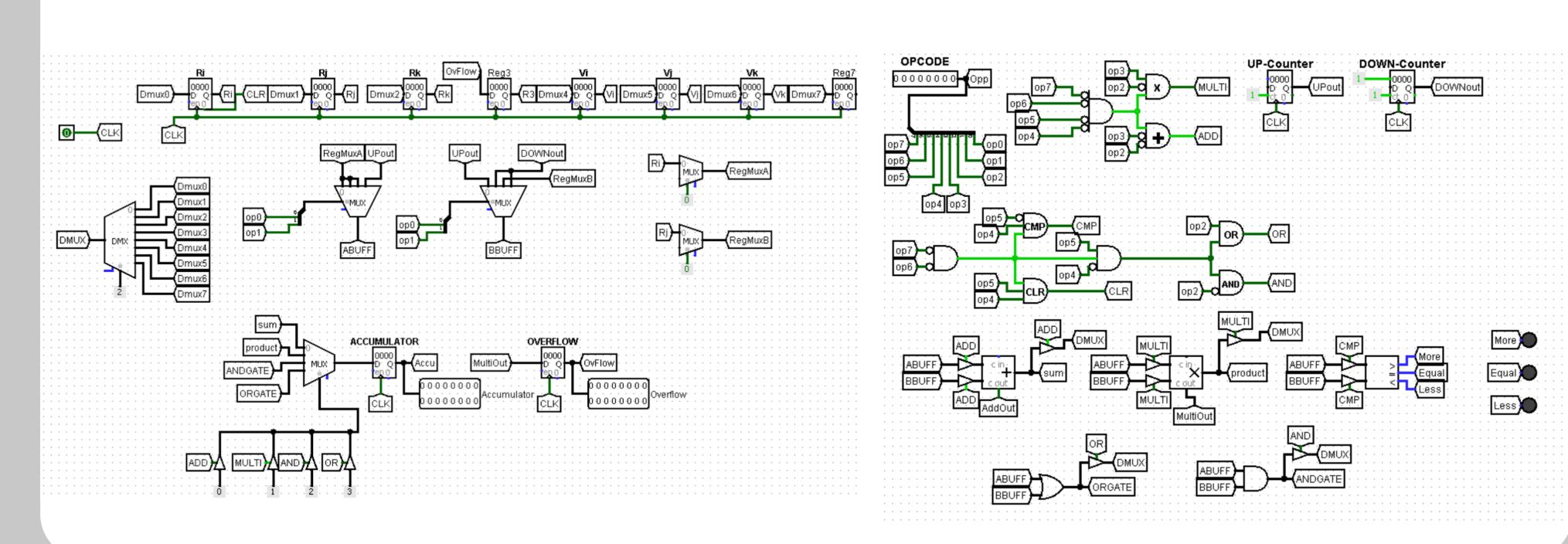

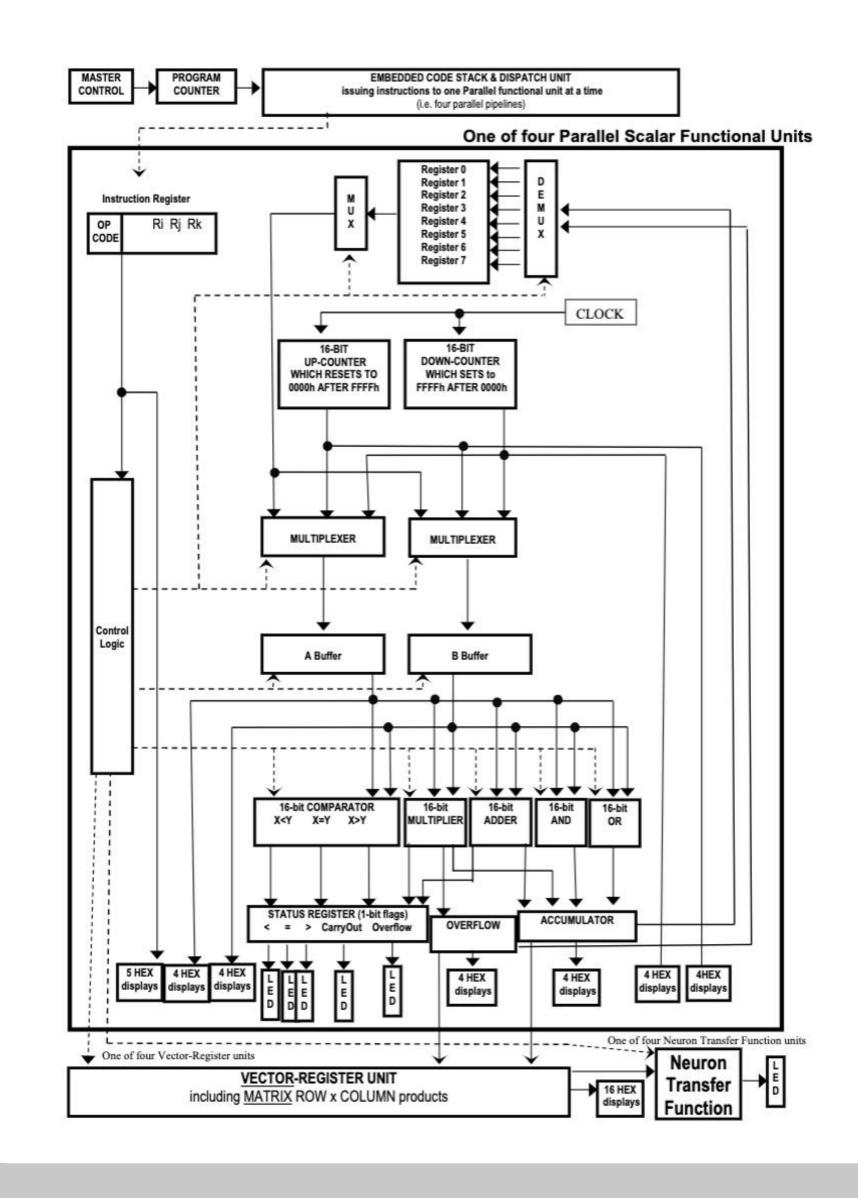

The overall design of the project involves a main code stack and dispatch unit as a part of a 4way processor unit. This means that the processor designed is capable of performing 4 operations at once. Additionally, the processor is capable of scalar and vector operations, these operations are being determined by the OP code that is specified in the design specifications for the project. The OP code is input into the project and then spread throughout the rest of the project to guide all of the actions taken.

## LOGISIM

Logisim comes prebuilt with a subcircuit function. This function allows circuits to be represented by a box with inputs and outputs. This allows for such a complex circuit to visible on a single screen.

# DESIGN SPECIFICATIONS

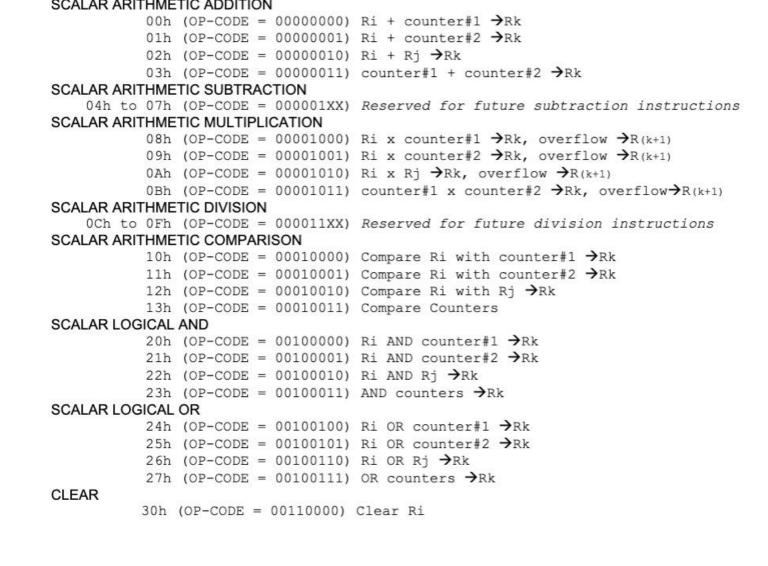

MACHINE INSTRUCTION SET

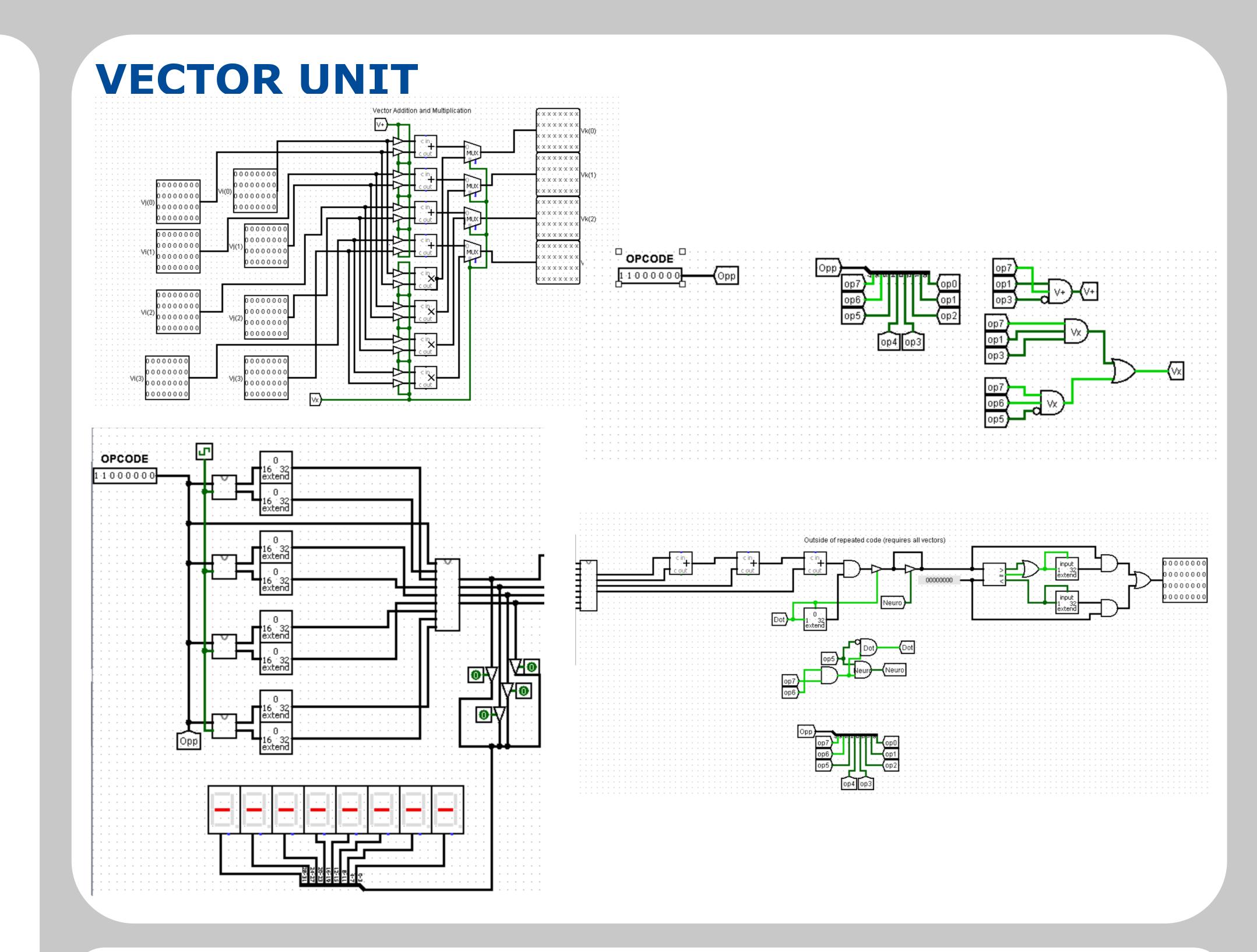

#### VECTOR/ARRAY / MATRIX and NEURON INSTRUCTIONS

VECTOR ARITHMETIC ADDITION

82h (OP-CODE = 10000010) Vi + Vj →Vk

VECTOR ARITHMETIC SUBTRACTION

84h to 87h (OP-CODE = 100001XX) Reserved for future subtraction instructions

VECTOR ARITHMETIC MULTIPLICATION

0Ah (OP-CODE = 10001010) Vi x Vj →Vk, overflow →V(k+1)

VECTOR ARITHMETIC DIVISION

8Ch to 8Fh (OP-CODE = 100011XX) Reserved for future division instructions

MATRIX ROW x COLUMN (i.e., Dot-Product)

C0h (OP-CODE = 11000000) Vi x Vj →Vk, overflow →V(k+1)

Vk(1)+Vk(2)+Vk(3)+Vk(4) → 32-Bit Scalar Accumulator

NEURON TRANSFER FUNCTION

E0h (OP-CODE = 11100000) Vi x Vj →Vk, overflow →V(k+1)

Vk(1)+Vk(2)+Vk(3)+Vk(4) → 32-Bit Scalar Accumulator

32-Bit Scalar Accumulator → Neuron Transfer Function

# SCALAR UNIT